Plaintext IP can be absorbed during synthesis as part of the top-level design. The Xilinx Vivado IP Catalog tool generates Xilinx IP in two forms: plaintext RTL, and encrypted RTL. The difference between a grey-box and white-box netlist in this context is that a white-box netlist can also be used in Absorb mode. The netlist output by synthesis doesn’t include the IP logic, which is added during place-and-route. The IP netlist is used for timing and resource estimation. The netlist output by synthesis doesn’t include the IP logic, which is added during place-and-route.Īltera offers a ‘grey-box’ flow, in which Altera tools generate a read-only netlist, which cannot be re-optimized, for the Synopsys Synplify tool. Synthesis has no visibility of IP timing or resources, unless special attributes are added to the stub. In a black-box methodology for gate-level IP, a stub for the IP is included in the design RTL. The netlist output by synthesis doesn’t include the IP logic, which is added during place and route. Synthesis does not change the IP, whose netlist is used for timing and resource estimation. In a white-box methodology for gate-level IP, the IP netlist is added as a read-only model. The netlist output by synthesis includes the IP logic, so there is no need to provide the IP separately to the place and route process.

In an Absorb methodology, the IP logic can be optimized as part of the larger design during synthesis. There are various ways in which IP can be incorporated in a design: by being absorbed into the design’s RTL, or incorporated as a white box, grey box or black box model.

Whether or not you want to optimise the contents of an IP block, and/or use the contents to develop good timing and resource estimates.Your IP integration strategy depends on a number of factors: IP is packaged in a number of ways, depending on three key parameters (see Figure 1):įigure 2 Comparing the features of RTL and netlist (Source: Synopsys) Choosing an IP integration methodology user requirements, such as QoR, visibility, and stability.

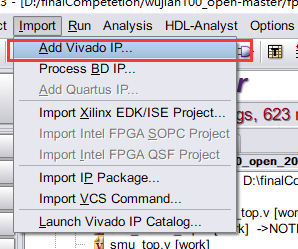

#Synplify pro vs vivado generator

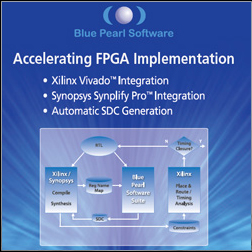

Tools such as Synopsys’ Synplify can ingest all the IP files created by an IP vendor’s generator tool and use them as input to its integration process. An IP packaging tool is necessary so that end users can generate the specific version of the IP they need, target it to their choice of FPGA, and get a licensed file for integration. More complex distribution strategies are necessary if creators are distributing configurable IP, targeting specific implementation technologies, or for licensing reasons. In the simplest IP creation process, a team develops an IP block, compresses the file and sends it to the design team, which unpacks it and integrates the RTL into the top level of its design, which is then synthesized and implemented as a whole.Ī slightly more complex approach sees the creation team including constraints with the RTL, which are then used to inform the place and route process. Optimised approaches to managing and using third-party IP, and packaging your own IP for reuse, can help ensure that methodology issues don’t undermine the advantages of using IP in FPGA-based designs. The combination of FPGAs and IP blocks enables teams to develop and try out complex designs quickly. How Synplify makes it easier to use IP in FPGA-based designs, and package your own IP for secure reuse, on Altera and Xilinx devices

0 kommentar(er)

0 kommentar(er)